基于多时钟的处理,在跨时钟域的处理上有优势

”_mclk multi_clock_domain 时钟域 跨_时钟_处理 跨时钟域“ 的搜索结果

跨时钟域问题(Clock_Domain_Crossing).doc

FIFO以及跨时钟域的同步问题。 FIFO有分离的地址总线和用以读写数据的数据通道,以及指示堆栈状态(满、将满等)的状态线。

外文经典跨时钟域处理.rar

标签: 跨时钟域

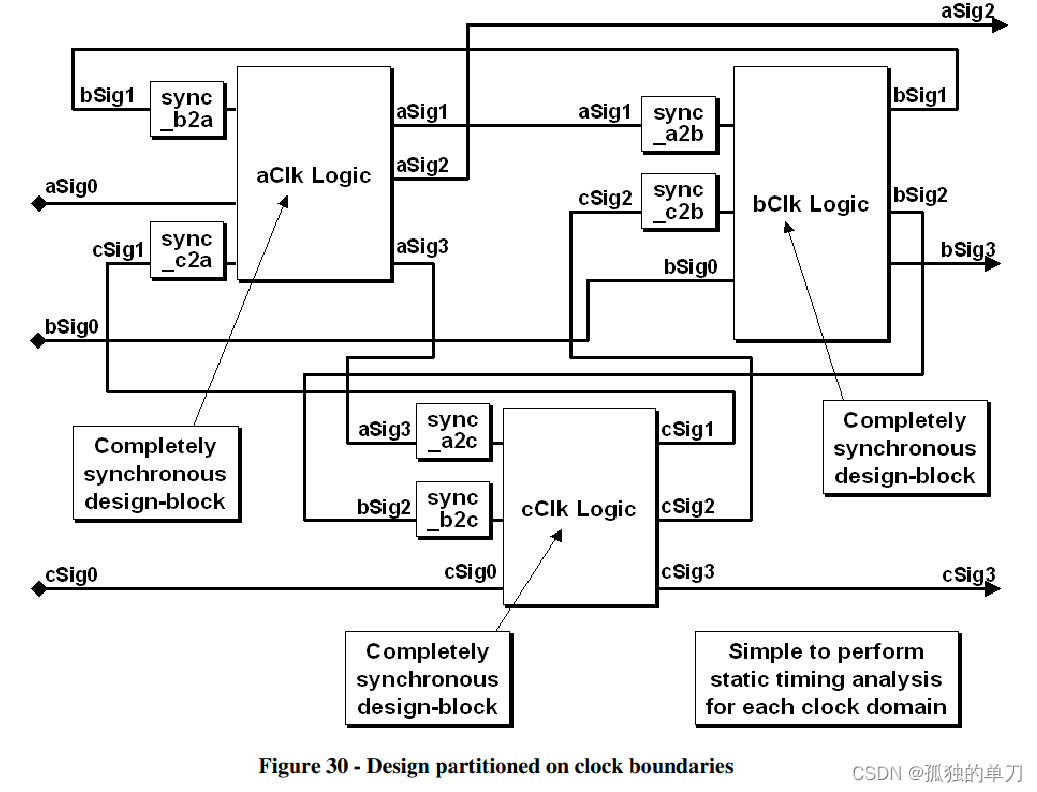

Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog 外文经典

基于SystemVerilog的跨时钟域设计与验证,翻译Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

CDC:跨时钟域处理

标签: CDC

CDC(clock domain crossing)检查(跨时钟域的检查)是对电路设计中同步电路设计的检查。非同步时钟没有固定的相位关系,这样Setup/Hold不满足而产生了亚稳态是无法避免的。我们采用同步设计的方法保证亚稳态不会...

描述跨clock domain 的处理,跨时钟域的。0000000000000000000000000000

并且,由跨时钟域处理不当引发的问题可能是偶现的,通常很难复现和定位问题。综上,CDC(Clock Domain Crossing,跨时钟域)处理,是数字设计中基本而又重要的一个课题。 亚稳态 信号输入触发器时,如果在时钟的触发...

跨时钟域(Clock Domain Crossing,CDC)约束适用于具有不同启动(launch)和捕获(capture)时钟的时序路径。 根据启动和捕获时钟关系以及在CDC路径上设置的时序例外(timing exception),分为同步CDC和异步CDC。 例如,被...

跨时钟域处理--最终详尽版

标签: IC

跨时钟域处理–最终详尽版 文章目录跨时钟域处理--最终详尽版1. 异步时序定义2. 亚稳态3. 单比特同步策略方法一:双锁存器注意问题1注意问题2注意问题34.多比特同步策略控制信号多比特同步同步变化的控制信号控制...

引言:设计者有时候需要将处于两个不同时钟域的系统对接,由于接口处是异步(会产生setuptime 和holdtime violation,亚稳态以及不可靠的数据传输)的,因此处理起来较同步逻辑更棘手,需要寻求特殊处理来进行接口...

推荐文章

- python怎么输出logistic回归系数_python - Logistic回归scikit学习系数与统计模型的系数 - SO中文参考 - www.soinside.com...-程序员宅基地

- VS2017、VS2019配置SFML_vsllfqm-程序员宅基地

- vc——类似与beyondcompare工具的文本比较算法源代码_byoned compare 字符串比较算法-程序员宅基地

- aetna java_pom.xml-程序员宅基地

- 生成随机数_<math.h>随机数-程序员宅基地

- Z-Blog编辑器支持ppt导入-程序员宅基地

- 基于Unity3D的相机功能的实现(六)—— 上帝视角(王者荣耀视角)_unity overlook-程序员宅基地

- 用mac的chrome浏览器调试Android手机的网页-程序员宅基地

- 树莓派GPIO简单操作_树莓派怎么读取gpio口上的信息-程序员宅基地

- 【汽车电子】浅谈车载系统QNX_车机qnx虚拟化软件系统架构-程序员宅基地